# **Network on a Chip** L.Stewart<sup>1</sup>, Milessa Jong<sup>2</sup> <sup>1</sup>Scholar,Monash University,Melbourne,Australia. <sup>2</sup>Scholar,RMIT University, Melbourne,Australia. leastewart04@gmail.com

Abstract: - A number of research studies have demonstrated the feasibility and advantages of Network-on-Chip (NoC) over traditional bus-based architectures. This whitepaper summarizes the limitations of traditional busbased approaches, introduces the advantages of the generic concept of NoC, and provides specific data about Arteris' NoC.

Keywords: - Network-on-Chip, System on Chip.

#### **1. INTRODUCTION**

By adding many computing resources such as CPU, DSP, specific IPs, etc to build a system in System-on-Chip, its interconnection between each other becomes another challenging issue. In most System-on-Chip applications, a shared bus interconnection which needs an arbitration logic to serialize several bus access requests, is adopted to communicate with each integrated processing unit because of its low-cost and simple control characteristics. However, such shared bus interconnection has some limitation in its scalability because only one master at a time can utilize the bus which means all the bus accesses should be serialized by the arbitrator. Therefore, in such an environment where the number of bus requesters is large and their required bandwidth for interconnection is more than the current bus, some other interconnection methods should be considered.

Such scalable bandwidth requirement can be satisfied by using on-chip packet-switched micro-network of interconnects, generally known as Network-on-Chip (NoC) architecture. The basic idea came from traditional large-scale multi-processors and distributed computing networks. The scalable and modular nature of NoCs and their support for efficient on-chip communication lead to NoC-based system implementations. Even though the current network technologies are well developed and their supporting features are excellent, their complicated configurations and implementation complexity make it hard to be adopted as an on-chip interconnection methodology. In order to meet typical SoCs or multi-core processing environment, basic module of network interconnection like switching logic, routing algorithm and its packet definition should be light-weighted to result in easily implemental solutions.

Whether you are using AXI, OCP, AHB or a proprietary protocol, Flex NoC Network on Chip (NoC) IP reduces the number of wires by nearly one half, resulting in fewer gates and a more compact chip floor plan. Having the option to configure each connection's width, and each transaction's dynamic priority, assures meeting latency and bandwidth requirements.IP configuration tool suite, design and verification can be done easily, in a matter of days or even hours.

### IJLTEMAS

### 2. BENEFITS OF ADOPTING NOCS

NoC links can reduce the complexity of designing wires for predictable speed, power, noise, reliability, etc., thanks to their regular, well controlled structure. From a system design viewpoint, with the advent of multi-core processor systems, a network is a natural architectural choice. A NoC can provide separation between computation and communication, support modularity and IP reuse via standard interfaces, handle synchronization issues, serve as a platform for system test, and, hence, increase engineering productivity

#### **3. BENEFITS OF ADOPTING NOC**

- Point-to-Point connections.

- Physical design viewpoint.

- NoC links can reduce the complexity of designing wires for predictable speed, power, noise, reliability, etc.

## 4. NOC ARCHITECTURE

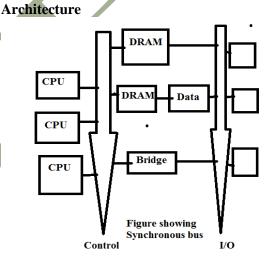

- Synchronous bus limitations lead to system segmentation and tiered or layered bus architectures.

- Modern Systems-on-Chip (SoCs) today contains hundreds of Intellectual Properties (IPs)/cores, including, programmable processors, co-processors, accelerators,

application-specific IPs, peripherals, memories, reconfigurable logic, and even analog blocks. We are now entered in the so called many-core era.

NoC provides enhanced performance (such as throughput) and scalability in comparison with previous communication

#### REFERENCES

[1] ITRS, International Technology Roadmap for Semiconductors 2004 Update, 2004.

[2] AMBA Specification Rev. 2.0, http://www.arm.com, 1999.

[3] Specification for the: WISHBONE System-on-Chip (SoC) Interconnection Architecture for Portable IP Cores, OpenCore, 2002.

[4] The Core Connect Bus Architecturehttp://www-03.ibm.com/chips/products/coreconnect/, 1999.

[5] A Comparison of Network-on-Chip and Busses, http://www.arteris.com/noc\_whitepaper.pdf, 2005.

[6] P. Guerrier and A. Greiner, A Generic Architecture for On-Chip Packet-Switched Interconnections, Proc. Design and Test in Europe (DATE), pp. 250-256, Mar. 2000,

[7] Douglas E. Comer (2000). Internetworking with TCP/IP – Principles, Protocols and Architecture (4th ed.). Prentice Hall. ISBN 0-13-018380-6. 2.4.9 – Ethernet Hardware Addresses, p. 29, explains the filtering.

[8] www.arteris.com.

[9]www.design-reuse.com/articles/10496/a-comparisonof-network-on-chip-and-busses.html

[10] Gram.eng.uci.edu/comp.arch/lab/NoCOverview.htm