## IJLTEMAS

# Logic Gates Using Self-Bias Transistors

Suraj Parkash<sup>1</sup>, Vikas Sindhu<sup>2</sup>

<sup>1</sup>M.Tech Student, Department of Electronics Engineering, Maharshi Dayanand University, Rohtak, Haryana, India <sup>2</sup>Assistant Prof., Department of Electronics Engineering, Maharshi Dayanand University, Rohtak, Haryana, India

*Abstract:* Power dissipation and is the contradicting factors in the design of VLSI CMOS devices. This review paper investigates CMOS circuits with SBT technique with the CMOS. Previous research on circuits shows reduction in power dissipation of combinational circuits by using other different techniques. A Self-bias transistor (SBT) is one which has its gate and drain connected together and works as a current-controlled switch. Here the gate voltage is provided by the drain and MOSFET is always in saturation. As long as a MOS transistor is in saturation region, the current is independent of the drain voltage and it behaves as an ideal current source. Thus power consumption is reduced. Extensive SPICE simulations will be performed with 0.18µm CMOS technology.

Keywords: CMOS circuits, Power dissipation, Propagation delay, Self-bias transistors (SBTs)

### I. INTRODUCTION

One of the key challenges in the integrated circuit industry is designing low-power circuits with high performance. Improving a design relative to power may slow down the circuit, but conversely, an improvement in speed may be achieved only at the expense of power [1].

Consistent with Moore's Law, the feature size of VLSI circuit technology is decreasing at a rate of 0.7 per generation. This rapid change in complexity and density of VLSI circuits gives rise to a number of design issues that were considered unimportant during the predeep-submicron era. The contribution of leakage or standby currents to the overall power consumption of a circuit is one such parameter. The contribution of leakage or standby currents to the overall power consumption of a circuit is one such parameter. While power consumption of a circuit is one such parameter. While power consumption has been a critical issue in today's VLSI circuits, much of the attention has focused on reducing its dynamic (or switching) component  $P_{SW}$ , which is given by

$$P_{SW} = \frac{1}{2} SC_L V_{DD}^2 f$$

(1)

Where S is the switching activity,  $C_L$  is the output capacitive load,  $V_{DD}$  is the supply voltage, and f is the frequency. Thus, reducing  $V_{DD}$  is a popular way of reducing  $P_{SW}$  due to its quadratic contribution. However, reducing the ratio of supply voltage to threshold voltage  $V_{th}$  increases the delay D of a circuit.

To overcome this effect, threshold voltages are being reduced as well [2]. However, lowering the threshold voltage causes standby currents to increase exponentially due to increased subthreshold conduction. Thus, leakage has become an important component in the power equation and will begin to dominate switching power as feature size continues to decrease [4]–[6]. One efficient method for reducing power dissipation is Self-bias Transistors (SBTs) connected between the pull-up/pull-down network and the supply rails. This technique is presented in [3].

### II. CMOS CIRCUIT DESIGN WITH SELF-BIAS TRANSISTORS

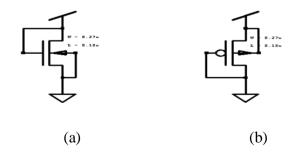

A SBT is one which has its gate and drain connected together and works as a current-controlled switch. Figure 1 shows a PMOS and NMOS SBT. Here the gate voltage is provided by the drain and MOSFET is always in saturation. As long as a MOS transistor is in saturation region, the current is independent of the drain voltage and it behaves as an ideal current source seen from the drain terminal. The current through a MOS device in saturation is given by equation

$$I_{dsat} = \frac{1}{2} k_n (V_{GS} - V_{th})^2$$

(2)

Where,  $k_n = k_n' (W/L)$  is the gain factor and  $k_n' = \mu_n C_{ox}$  is the process transconductance of the device.  $V_{GS}$  is the gate to source voltage and  $V_{th}$  is the threshold voltage of the transistor. Thus by controlling the current through the SBTs we can control the charging and discharging of the load capacitance and hence the dynamic power dissipation which is due to the charging and discharging of the capacitor.

$$C = \frac{1}{V_{DD}} \int I dt$$

(3)

$$P_{dyn} = CV_{DD}f^2$$

(4)

Figure 1: (a) NMOS SBT (b) PMOS SBT

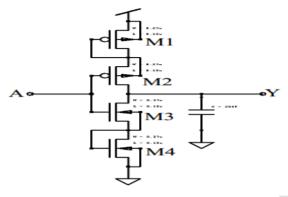

Figure 2 shows a CMOS inverter with SBT connected. M1 and M4 are the PMOS and NMOS SBTS respectively. During the active mode, either the NMOS (or PMOS) SBT power gates the pull-down (or pull-up) logic and reduces the leakage current. By adding the SBTs in the

### Volume III, Issue VIII, August 2014

IJLTEMAS

conventional CMOS circuit the effective on resistance got increased. The effective on resistance is given by the equation

$$R_{\rm ON} = \frac{1}{\Lambda I_{\rm D}} \tag{5}$$

Thus with increase in  $R_{ON}$ ,  $I_D$  will decrease and hence there is a decrease in leakage current. Table 1 shows the power dissipation and propagation delay of with and without SBT connected. It shows that there is a considerable decrease in power. However the propagation delay gets increased.

Figure 2: Inverter with SBTs

#### REFERENCES

- [1]. Vignesh Subbian and Fat Duen Ho, "Power-delay trade-offs in CMOS circuits using self-bias transistors", Department of Electrical and Computer Engg, University of Alabana, Huntsville.

- [2]. Kamal S. Khouri, Member, IEEE, and Niraj K. Jha, Fellow, IEEE, "Leakage Power Analysis and Reduction During Behavioral Synthesis" *IEEE Transactions on very large scale integration(VLSI) systems, Vol. 10, No. 6, Dec 2002.*

- [3]. H Gopalakrishnan and W Shuie, "Leakage power reduction using self-bias transistor in VLSI circuits" *IEEE Workshop* on Microelectronics and Electron Devices, pp. 71-4, 2004.

- [4]. Kaushik Roy, Fellow IEEE, Saibal Mukhopadhyay, Student Member IEEE and Hamid Mahmoodi-Meimand, Student Member IEEE "Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits" in *Proc. of the IEEE*, Vol 91, No. 2, Feb 2003.

- [5]. A. Chandrakasan, I. Yang, C. Vieri, and D. Antoniadis, "Design considerations and tools for low-voltage digital design," in *Proc. Design Automation Conf.*, June 1996, pp. 113–118.

- [6]. R. X. Gu and M. I. Elmasry, "Power dissipation analysis and optimization of deep submicron CMOS digital circuits," *IEEE J. Solid-State Circuits*, vol. 31, pp. 707–713, May 1996.

- [7]. M. C. Johnson, D. Somasekhar, and K. Roy, "Models and algorithms for bounds on leakage in CMOS circuits," *IEEE Trans. Comput.-Aided Design*, vol. 18, pp. 714–725, June 1999.

- [8]. S. Mutoh, T. Douseki, Y. Matsuya, T. Aoki, S. Shigematsu, and J. Yamada, "1-V power supply high-speed digital circuit technology with multi-threshold-voltage CMOS," *IEEE J. Solid-State Circuits*, vol. 30, pp. 847–854, Aug. 1995.

- [9]. J. Kao, A. Chandrakasan, and D. Antoniadis, "Transistor sizing issues and tool for multi-threshold CMOS technology," in *Proc. Design Automation Conf.*, June 1997, pp. 409–414.