# Design of an Efficient Frequency Synthesizer used For Multi-Band OFDM

Ananda M<sup>#</sup>, Dr. A B Kalpana<sup>\*</sup> <sup>#</sup>ECE Department, PESIT-BSC, Bangalore, India-560100 <sup>\*</sup>ECE Department, BIT, Bangalore, India-560004

Abstract— This journal describes the design of a 3GHz -10 GHz [1] frequency synthesizers for Multi-band OFDM in an Ultrawide band (UWB) transceiver at 180nm CMOS technology. As there is a requirement of high speed data rate, reduction in chip size and low power consumption for wireless devices there is demand for high speed complex signal processing architecture which meet the requirements. Bandwidth is another precious commodity, according to FCC regulations available unlicensed bandwidth is 3.1GHz - 10.6GHz [1] (UHB). In this journal the system requirements for the Frequency synthesizer in an Ultrawide band (UWB) is discussed. OFDM is combination of modulation and multiplexing, the signal which is to be sent through channel is first split into independent sub channels, modulated by data at transmitter and then de-multiplexed at the receiver. In this process the frequency synthesizer generates carrier tone for each sub channel. Data which is to be transferred is split using multiplexer and can be transferred in each band separately and combined at the receiver. The number of RF blocks are implemented for generating carrier tones. 14 carrier tones are generated to reduce power consumption, to increase the data rate. An efficient frequency synthesizer is proposed to reduce number of RF blocks. The efficient system could be used for high data rate communication system like 3G, 4G and other applications which require high data rate.

*Keywords*— Frequency Synthesizer, Ultra-Wide Band, OFDM, Radio Frequency, TSPC.

#### I. INTRODUCTION

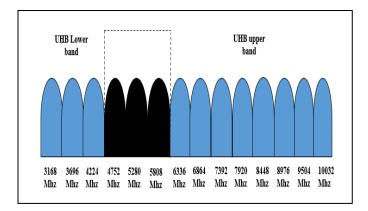

A s the technology goes on improving there is demand for high speed data rate signal processing applications. FCC (Federal Communications Commission) in the year 2002 released unlicensed UHB band in the range 3.1 GHz to 10.6 GHz [1], bandwidth is the precious commodity so we need to utilize available bandwidth to achieve high data rate. Multiband OFDM is one of the most efficient systems to effectively utilize available bandwidth, increase high data rate. Frequency synthesizer generates different carrier tones in the range 3-10 Hz range. This technique divides the available bandwidth into 14 different channels with each of 528MHz as shown in Fig.1. This system provides good flexibility for frequency regulation and can co-exist with 802.11a/b/g wireless systems [2].

Many papers have discussed Multi-band OFDM but have used many local oscillators to generate a different frequency which occupies more area so the cost of the system increases. This is the most effective system where 14 bands, 14 different carrier tones are generated with the help of single fixed oscillator which will reduce the area hence the size and the cost of the die reduces. OFDM is a technique where the available bandwidth is divided into independent channels, the signal which is to be sent through channel is split and multiplexed and sent to different channels, re-multiplexed at the receiver and thus high data rate is achieved.

This system uses Frequency Dividers, Frequency Subtractors and Frequency Adders to generate 14 different bands. The following sections describe about Frequency planning and proposed architecture. Section II describes Frequency planning and proposed architecture. Section III describes Frequency synthesizer blocks. Section IV describes frequency synthesizer simulation results. Section V describes conclusion of the system.

#### II. PROPOSED ARCHITECTURE FOR FREQUENCY SYNTESIZER

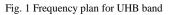

Frequency synthesizer generates carrier tone for both upconversion and down-conversion in multiband UHB transceiver. The role of frequency synthesizer is illustrated in Fig. 2.

Fig.2 Frequency Synthesizer in Multiband UHB Transceiver [1]

Table 1 shows the frequency Synthesis for Multiband OFDM transceiver. The reference frequency Fref is chosen to be 8448MHZ to generate 14 frequency tones. The bandwidth of each frequency sub-band is 528MHz. Frequency division, Frequency addition and Frequency subtraction is done to obtaining various carrier tone from reference frequency as shown in Table1.

Table - 1 Frequency Synthesis for the 14 Carrier Tones

| Band | Carrier Tone (MHz) | Frequency Synthesis                          |  |  |

|------|--------------------|----------------------------------------------|--|--|

| 1    | 3168               | Fref/2 - Fref/16 - Fref/16                   |  |  |

| 2    | 3696               | Fref/2 – Fref/16                             |  |  |

| 3    | 4224               | Fref/2                                       |  |  |

| 4    | 4750               | Fref/2 + Fref/16                             |  |  |

| 5    | 5280               | Fref/2 + Fref/16 +Fref/16                    |  |  |

| 6    | 5808               | Fref/2 +Fref/16 + Fref/16 + Fref/16          |  |  |

| 7    | 6336               | Fref - Fref/16 - Fref/16 - Fref/16 - Fref/16 |  |  |

| 8    | 6864               | Fref - Fref/16 - Fref/16                     |  |  |

| 9    | 7392               | Fref – Fref/16 – Fref/16                     |  |  |

| 10   | 7920               | Fref – Fref/16                               |  |  |

| 11   | 8448               | Fref                                         |  |  |

| 12   | 8976               | Fref + Fref/16                               |  |  |

| 13   | 9504               | Fref + Fref/16 + Fref/16                     |  |  |

| 14   | 10032              | Fref + Fref/16 + Fref/16 + Fref/6            |  |  |

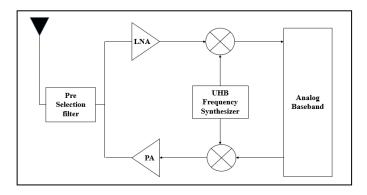

Proposed Frequency Synthesizer for generating different carrier tones is shown in Fig.3 which consists of four dividers, three adders and six subtractors circuits. Due to reduction in PLLs, number of RF blocks area consumed is reduced this reduces the cost of the system.

Obtaining the various frequencies are shown in Fig.3. The reference frequency 8448MHz is given to 4 divider circuit to obtain frequencies 4224MHz, 2122MHz, 1056 MHz and 528MHz. The reference frequency is added with consecutive frequency adder circuit to obtain 8712 MHz, 9504 MHz and 10032 MHz, again reference frequency 8448MHz is send to consecutive subtractor to get 7920MHz, 7392MHz, 6864 MHz The output of first frequency divider 4224MHz is subtracted with 2 frequency subtractor circuit to get 3696MHz and 3168MHz, again 4224MHz is added with 528MHz to get 4752MHz to get 4752MHz, 5280 MHz and 5808 MHz as shown in Fig.3.

Fig. 3 Proposed Multiband Ultra-Wide Band Synthesizer architecture.

# III. BASIC BLOCKS OF FREQUENCY SYNTHESIZER

# A. The Divider

Frequency divider is employed for high speed complex signal processing applications. Divider circuit plays a crucial role in generating various carrier tones from single fixed oscillator. Either the sinusoidal or pulsed signal can be divided to produce various frequencies according to the application. There are various types of frequency divider circuit present like flip flop based divider, TSPC based divider and regenerative divider. Regenerative divider consists of many numbers of passive components so that area consumption and cost increases. Flip flop based divider [2] uses number of transistors so the power consumption, area could be more. TSPC based frequency divider is the most advantage frequency for high speed applications because of less number of transistor, low power consumption, has only one input and the frequency range for operation is in Gigahertz.

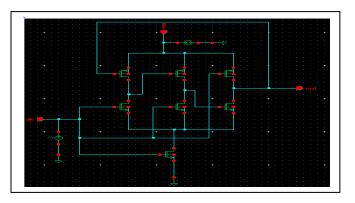

TSPC based divider circuit shown in figure 4 consists of three pmos and four nmos transistors. It operates in two modes evaluation mode and hold mode. If input is in positive cycle divider operates in evaluation mode, if input is in negative cycle divider operates in hold mode where output doesn't change. Divider by two operations with the help of Fig.4.

Fig .4 Frequency divider circuit.

### B. The Adder

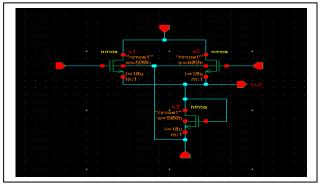

Frequency adder is one of the most important circuit in Analog design in generating different frequencies. Different carrier tones can be generated with the help of frequency adder circuit. Frequency adder circuit adds up the two signals which is given as input and produces output. Adder circuit is as shown in Fig.5 consists of three transistors. Frequency adder has less number of transistor which reduces area and power consumption.

Fig. 5 Frequency Adder circuit

## C. The Subtractor

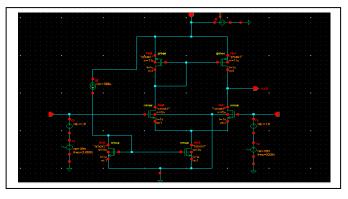

Frequency Subtractor is one of the important analog component in generating different frequency. Different carrier tones can be generated with the help of Subtractor. Frequency Subtractor produces the difference of two signals. There are various types of frequency Subtractor circuit like differential amplifier mixer could be used as Subtractor. Differential amplifier is one of the simplest Subtractor circuit is as shown in Fig.6

Fig .6 Frequency Subtractor circuit.

## IV. FREQUENCY SYNTHESIZER SIMULATIONS

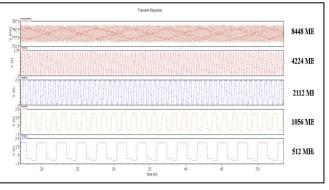

The frequency synthesizer is simulated in 180nm CMOS technology with the supply of 1.8V DC. Fig.7 shows the output waveforms obtained by Frequency divider by two circuits. The input frequency to the divider circuit 8448MHz is divided into 4224MHz, 2112MHz, 1056MHz and 528MHz.

Fig. 7 Simulation results of Frequency Divider

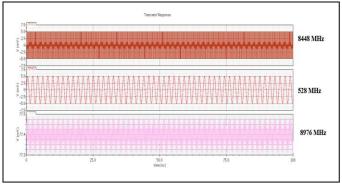

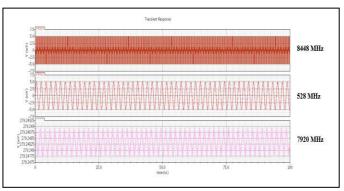

Figure 8 below shows the output waveforms of frequency adder circuit generating frequency of 8976MHz from 8448MHz and 528MHz

Fig .8 Simulation results of Frequency Adder

The Fig.9 shows the output waveform of Frequency Subtractor circuit, 8448MHz and 528MHz is given as input to frequency subtractor to obtain 7920 MHz.

Fig .9 Output waveform of Frequency Subtractor

Table-2 Comparison table of Reference papers

| Parameter          | [3]            | [1]                | [4]      | This work       |

|--------------------|----------------|--------------------|----------|-----------------|

| Frequency<br>range | 3 to 10<br>GHz | 3.1 to 10.6<br>GHz | 3.1-8GHz | 3.1 to 10.6 GHz |

| Power              | 1.5V           | 1.8V               | 1.8 V    | 1.8V            |

| supply             |       |       |       |       |

|--------------------|-------|-------|-------|-------|

| Current at<br>Vdd  | 59mA  | 65mA  | 90 mA | 51mA  |

| Number of<br>Bands | 9     | 14    | 14    | 14    |

| Feature<br>Size    | 180nm | 180nm | 180nm | 180nm |

#### V. CONCLUSION

Frequency Synthesizer for Muti-band OFDM is designed and analysis is done. Frequency synthesizer generates 14 bands in the range 3-10 GHz forming 14 carrier tones. The number of RF blocks is reduced which reduces area and power consumption. The average power consumption is 51mw. Proposed system and simulation result shows low cost, low power consumption.

#### ACKNOWLEDGMENT

I would like to express sincere gratitude to the institute PESIT-BSC for providing me with a conductive environment and BIT for research facilities that helped me a lot in completing this work. I would also thank the department of ECE for co-operating with me. I owe my deep sense of gratitude to my PhD guide Dr A B Kalpana, Associate Professor who has been very supportive and helped me in all possible ways to make this successful piece of work.

#### REFERENCES

- Xubo Wang and Anh Dinh have proposed Design of a 11-Band 3-10GHz Frequency Synthesizer for Multi-Band OFDM UWB Transceiver in 90nm CMOS Technology *IAENG International Journal of Computer Science*, 37:4, IJCS\_37\_4\_12.

- [2] Hui Zheng and Howard C. Luong have proposed A 1.5 V 3.1 GHz8 GHz CMOS Synthesizer for 9-Band MB-OFDM UWB Transceivers IEEE JOURNAL OF SOLID-STATE CIRCUITS,

VOL.42, NO. 6, JUNE 2007V Sharma, Dual Band Circularly Polarized Modified Rectangular Patch Antenna for Wireless Communication, *IEEE International Symposium on Antennas and Propagation and USNC/URSI National Radio Science Meeting*, Charleston, USA, **2009**, 1, 786-789.

- [3] Chinmaya Mishra, Alberto Valdes-Garcia, Edgar Sanchez-Sinencio and Jose Silva-Martinez have proposed Frequency Planning and Synthesizer Architectures for multiband OFDM UWB Radios IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 53, NO. 12, DECEMBER 2005.

- [4] Che-Fu Liang, Shen-Iuan Liu, Yen-Horng Chen, Tzu-Yi Yang and Gin-Kou Ma have proposed A 14-band Frequency Synthesizer for MB-OFDM UWB Application ISSCC 2006 / SESSION 6 / UWB TRANSCEIVERS / 6.7

- [5] Siavash Heydarzadeh and Pooya Torkzadeh have proposed A 12Ghz Fractional-n Extended TSPC Frequency Dividers Using 0.18μm CMOS Technology World Applied Sciences Journal 26 (6):755-763, 2013 ISSN 1818-4952.

- [6] Behzad Razavi, "RF Transmitter Architectures and circuits", IEEE Custom Integrated Circuits Conference, pp 197-204, 1999..

- [7] Behzad Razavi, "Design of Analog CMOS Integrated Circuits", Tata Mc Graw-Hill edition, pp100-126, 2002.

- [8] Behzad Razavi- "RF Microelectronics", Prentice hall Inc. 2nd Edition, 1998.

- [9] Thomas H Lee, "Design of CMOS Radio Frequency Integrated Circuits", Cambridge University Press, pp404-437, 1998.

- [10] Douglas A Pucknell and Kamran Eshraghian, "The Design of CMOS Radio Frequency Integrated Circuits", New York Cambridge University Press, pp25-55, 2008.

- [11] Ankita Tijare, Shweta Dhondse, Swati Nitnaware and Mahesh Pawar have proposed Low-Voltage, High Frequency CMOS Analog Multiplier International Journal of Engineering and Computer Science ISSN: 2319-7242 Volume- 3 Issue -3 March, 2014 Page No. 5004-5007.

- [12] http://www.cadence.com/

- [13] http://www.ncjrs.gov/pdf\_files/nij/191160.pdf.

- [14] http://www.cadence.com/rl/Resources/datasheets/virtuosovls XLds.pdf

- [15] <u>http://www.cadence.com/rl/resources/datasheets/virtuoso vse fam</u> <u>ds.pdf</u>

- [16] http://www.tufts.edu/rwhite07/PRESENTATIONS REPORTS/layout.pdf

- [17] http://www.ncjrs.gov/pdffiles1/nij/191160-b.pdf.